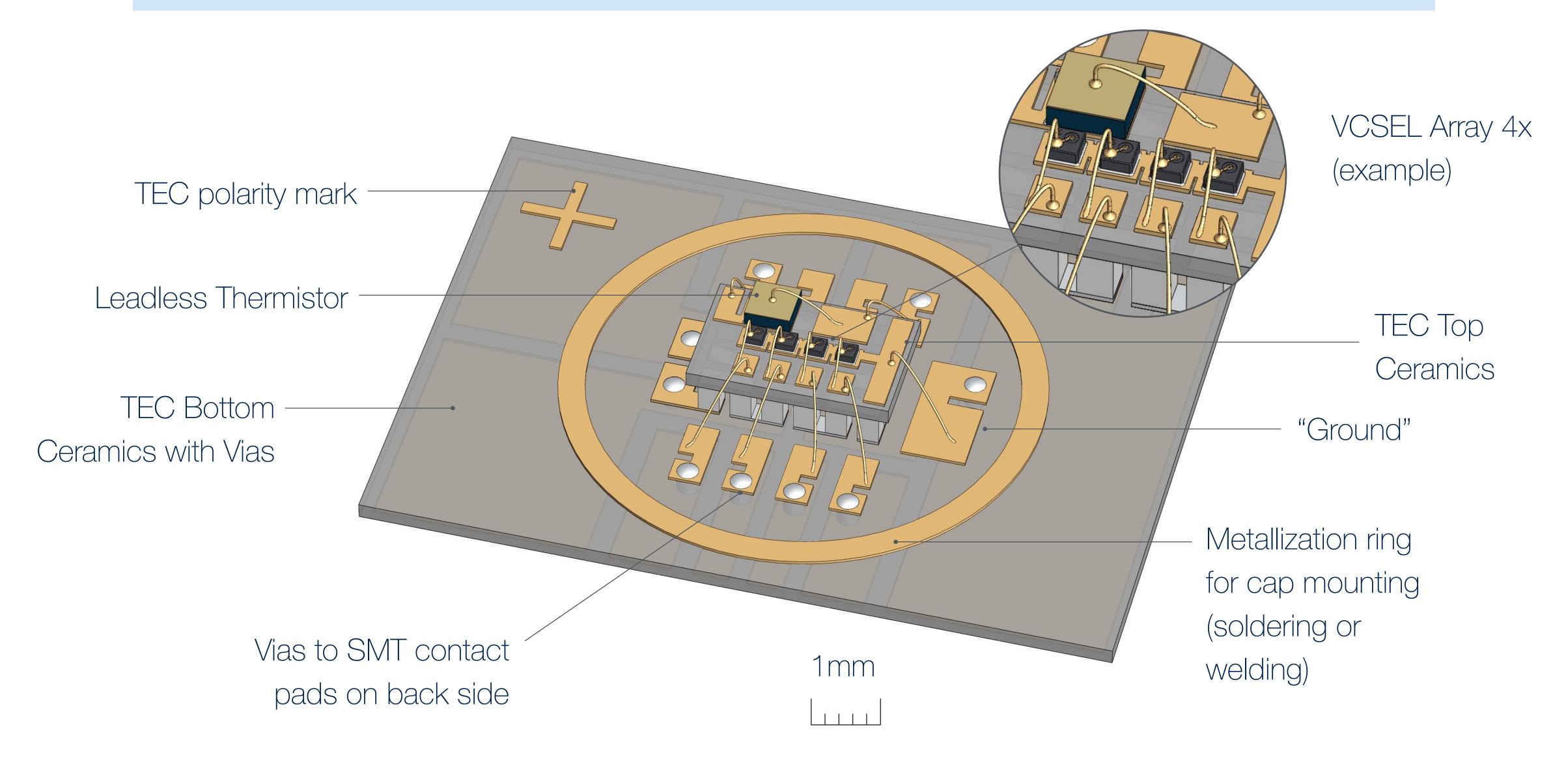

#### Header-free Solution for VCSEL Applications

TEC Bottom Ceramics is revised for SMT process (using Vias)

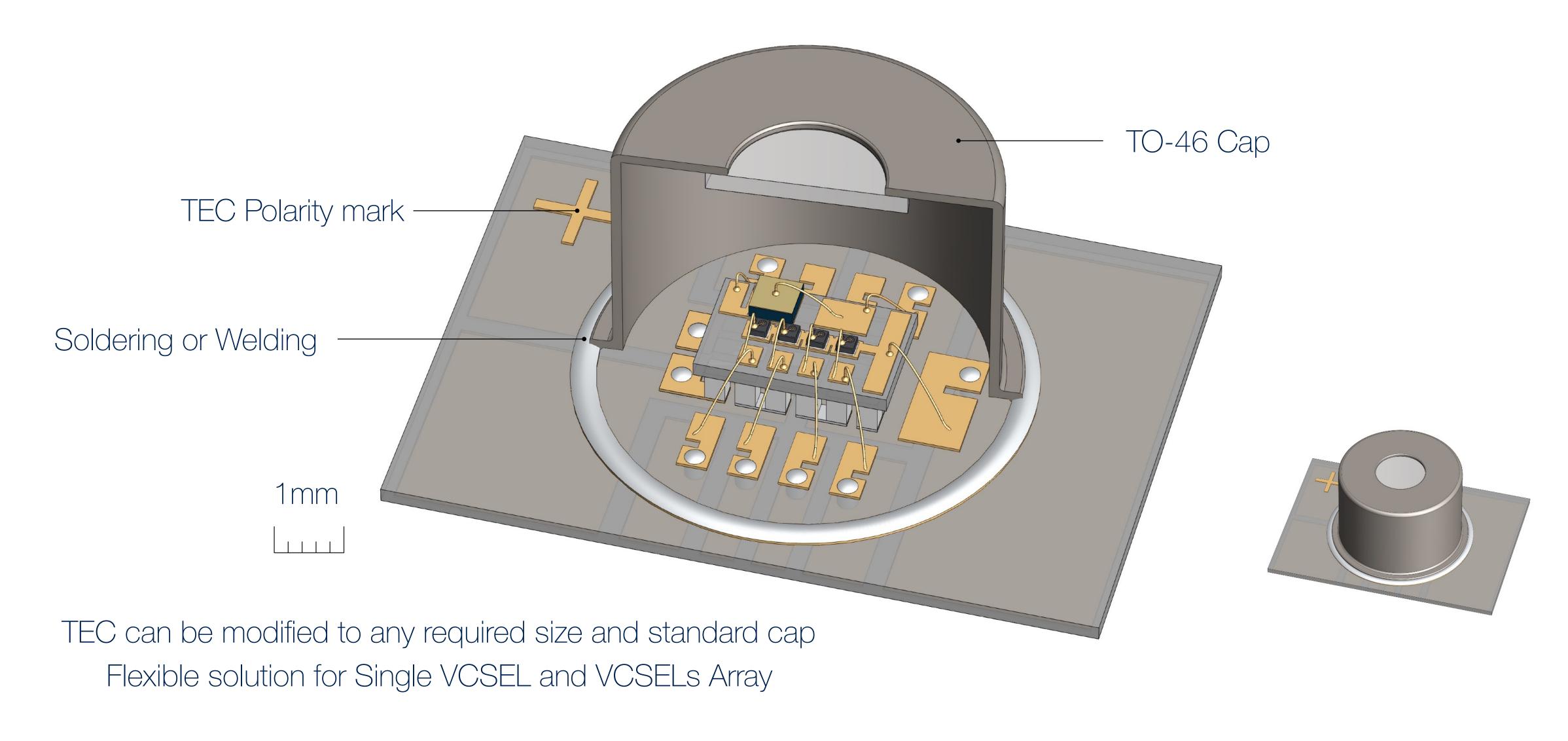

Flexible solutions for single VCSEL and Arrays

Various TEC solutions with different performance parameters

# Header-free Solution for VCSEL Applications (Example)

### Header-free Solution for VCSEL Applications

## Header-free Solution for VCSEL Applications

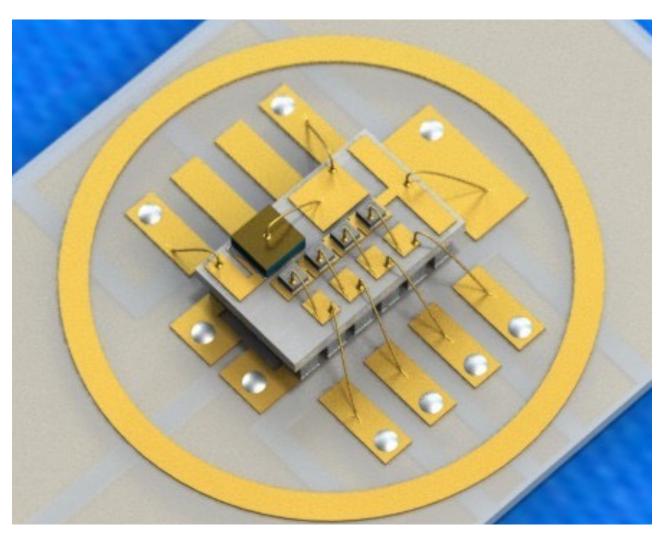

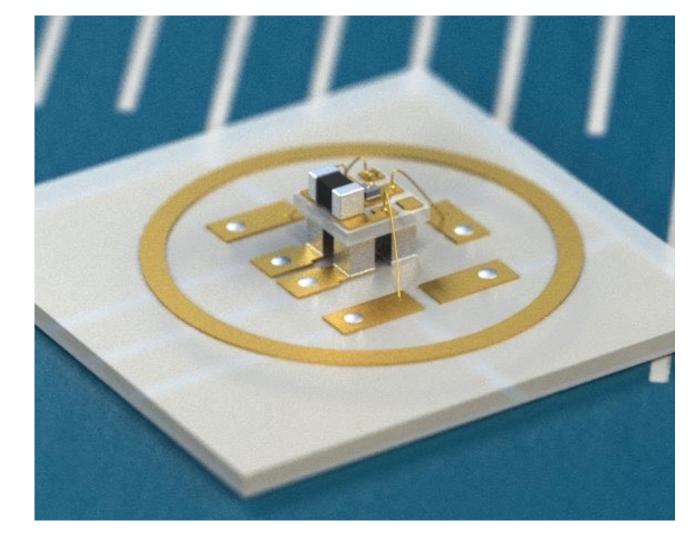

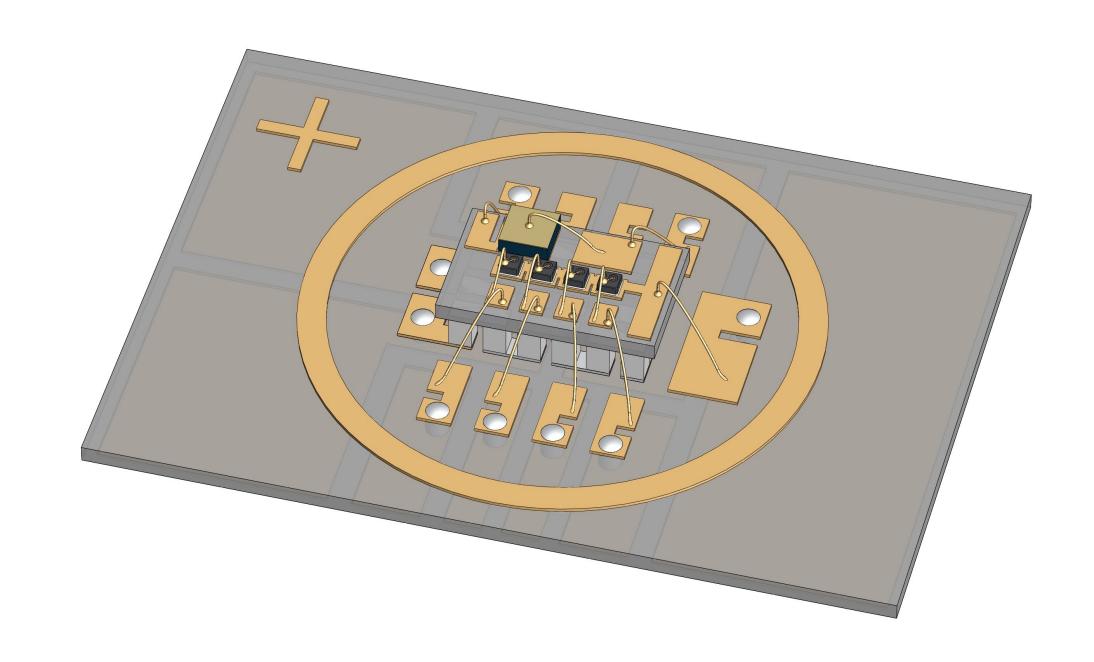

VCSEL TEC Example Assembly

TEC Bottom Ceramics is suitable for SMT mounting.

VIAS, pinout, TEC type are variable

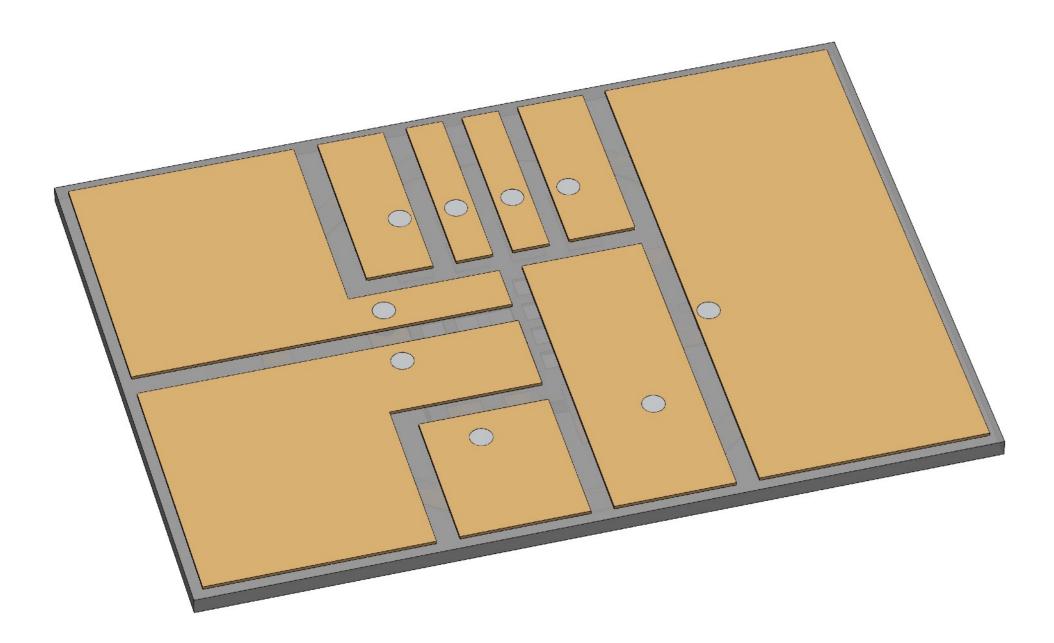

Bottom side layout (example)

SMT surface can be developed in accordance to application requirements (size, number of vias and etc)

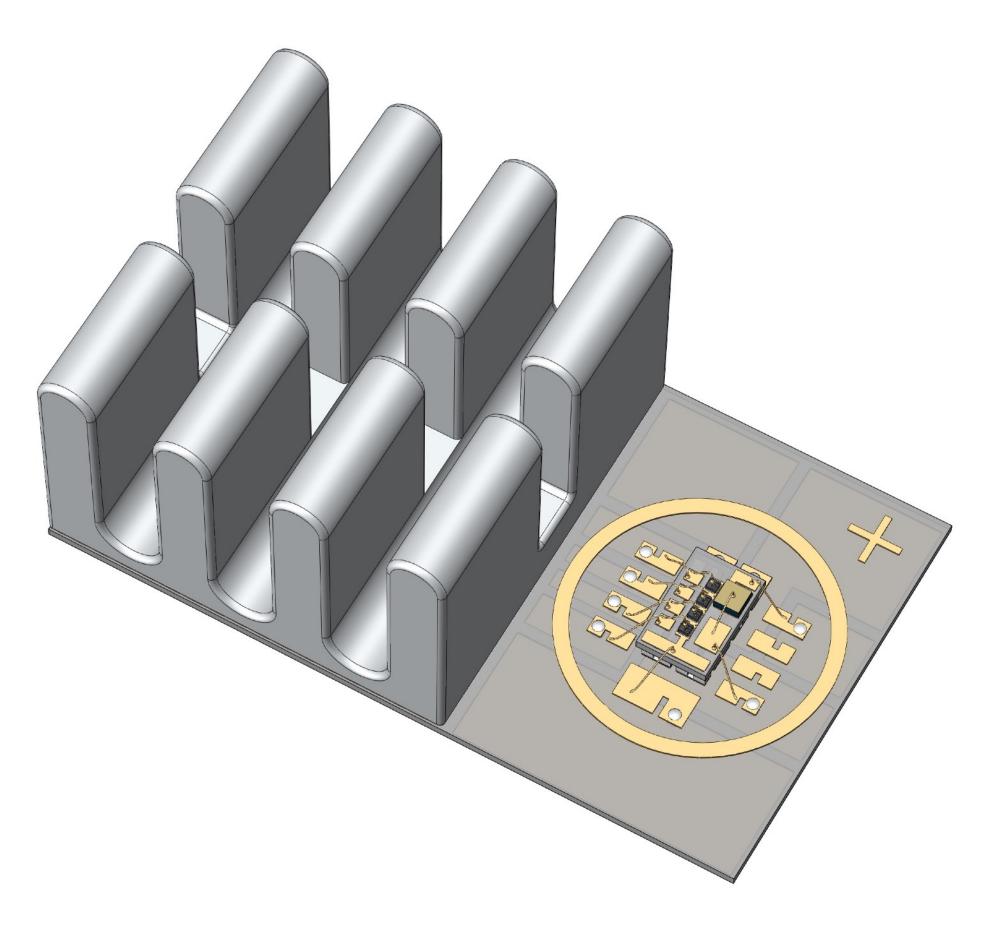

#### Variable Modification with Heatsinks

Extended Ceramics for standard 7x7x4mm³ Heatsink mounting

Copyright TEC Microsystems GmbH. Images by Tim Gromov. Images contain hidden watermarks.

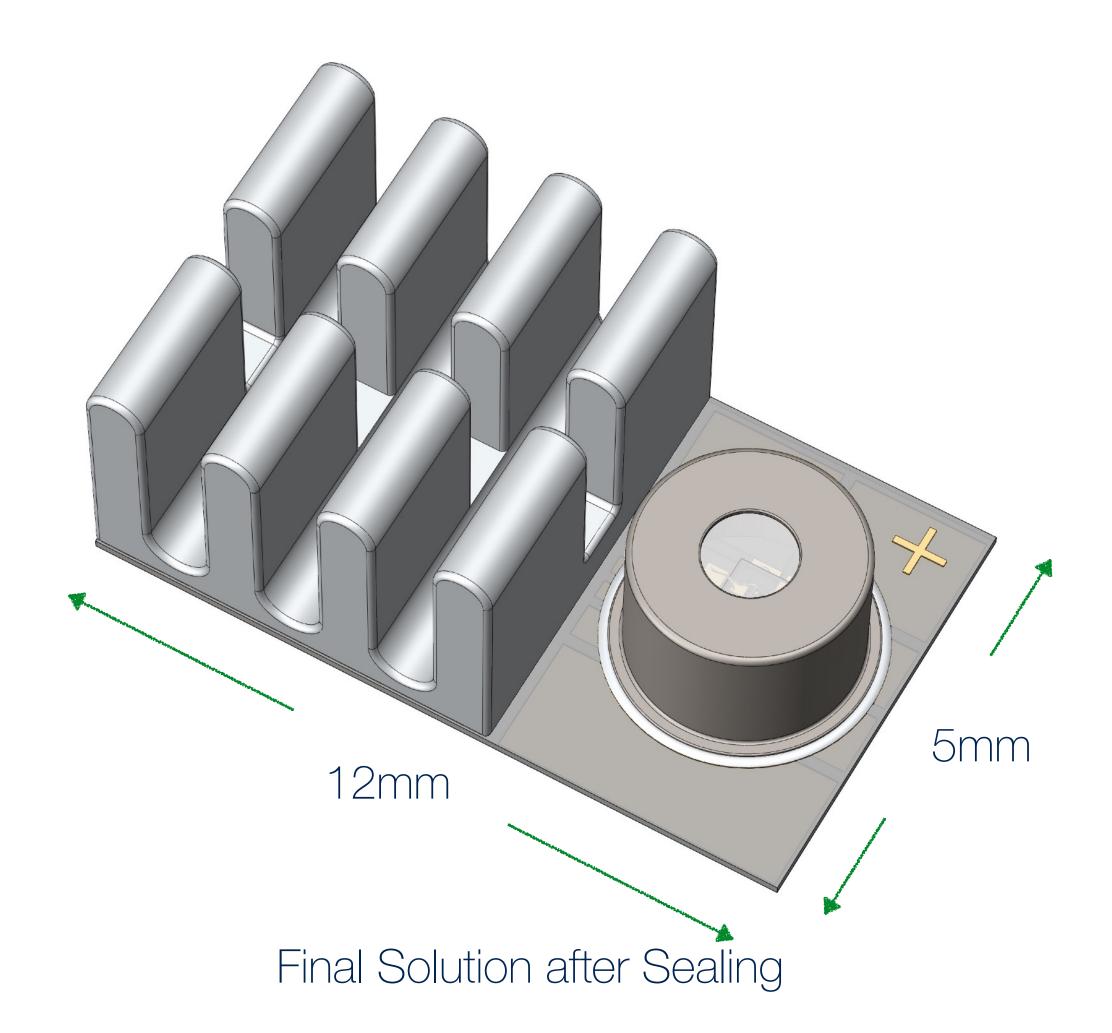

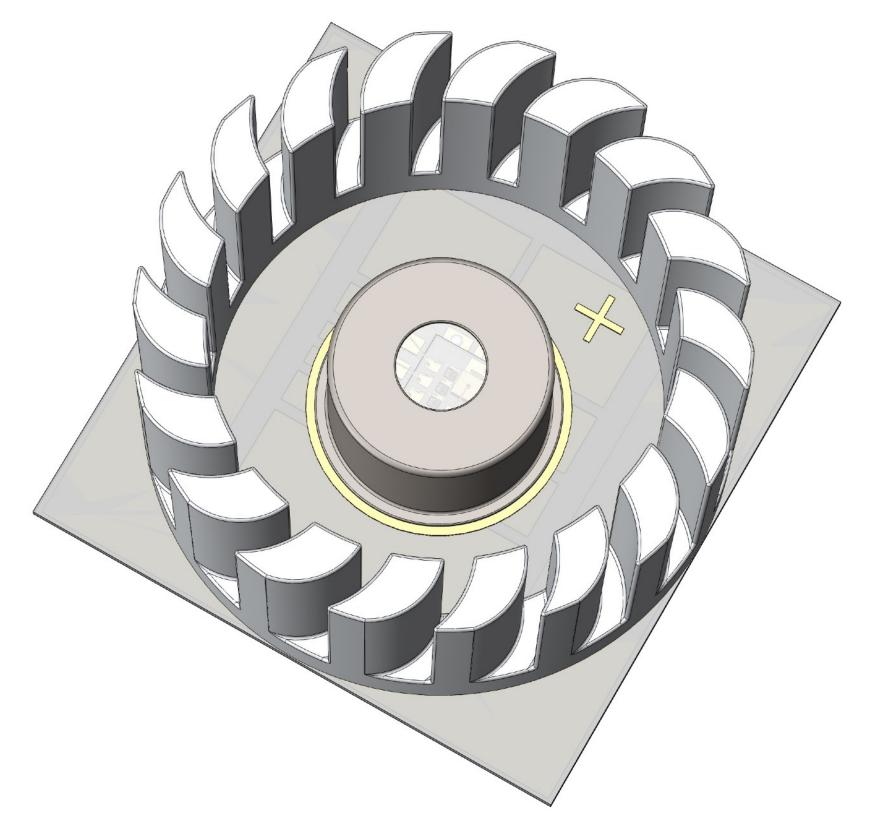

#### Variable Modification with Heatsinks - Radial Heatsink (Example)

Extended Ceramics for customized 10mm dia Radial Heatsink

Final Solution after Sealing

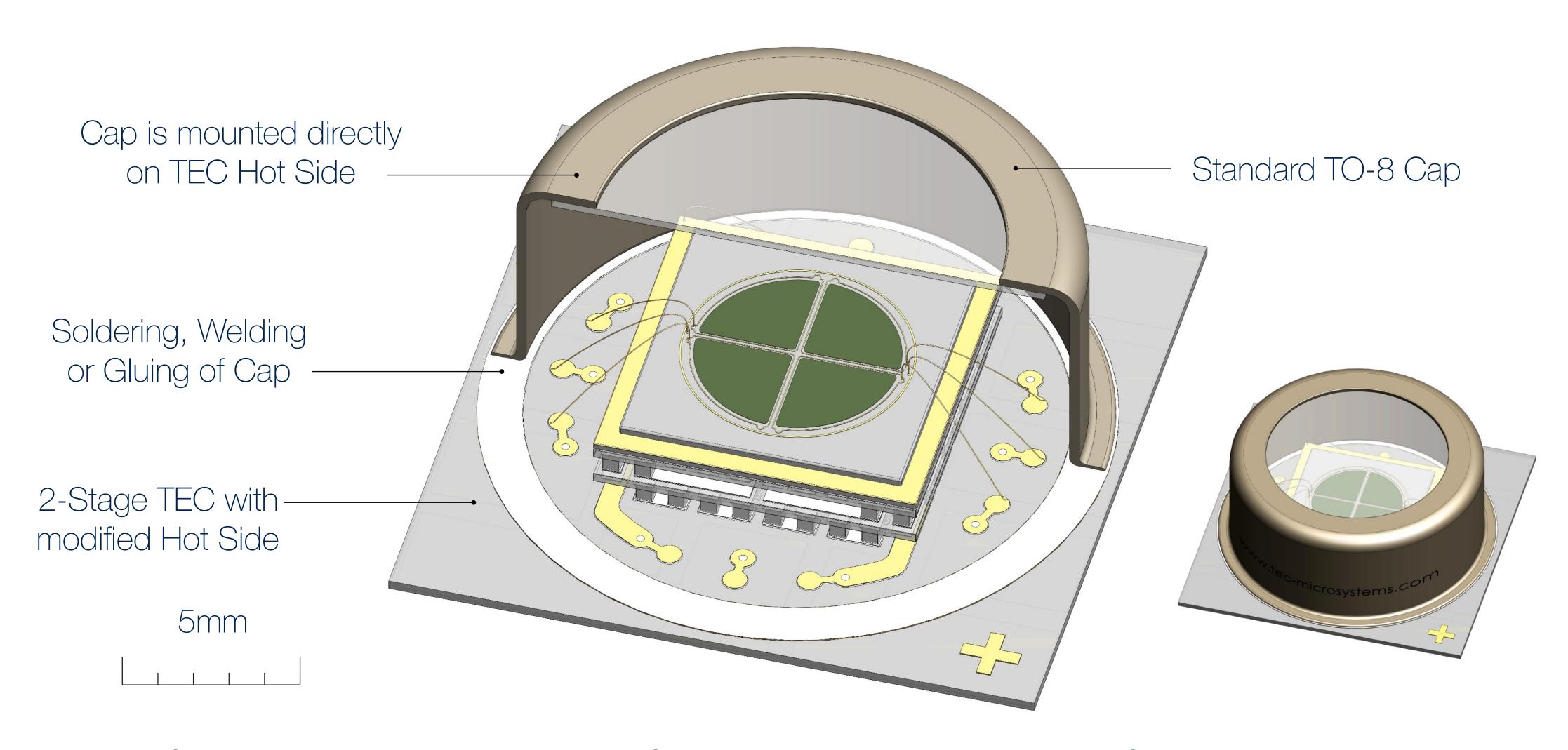

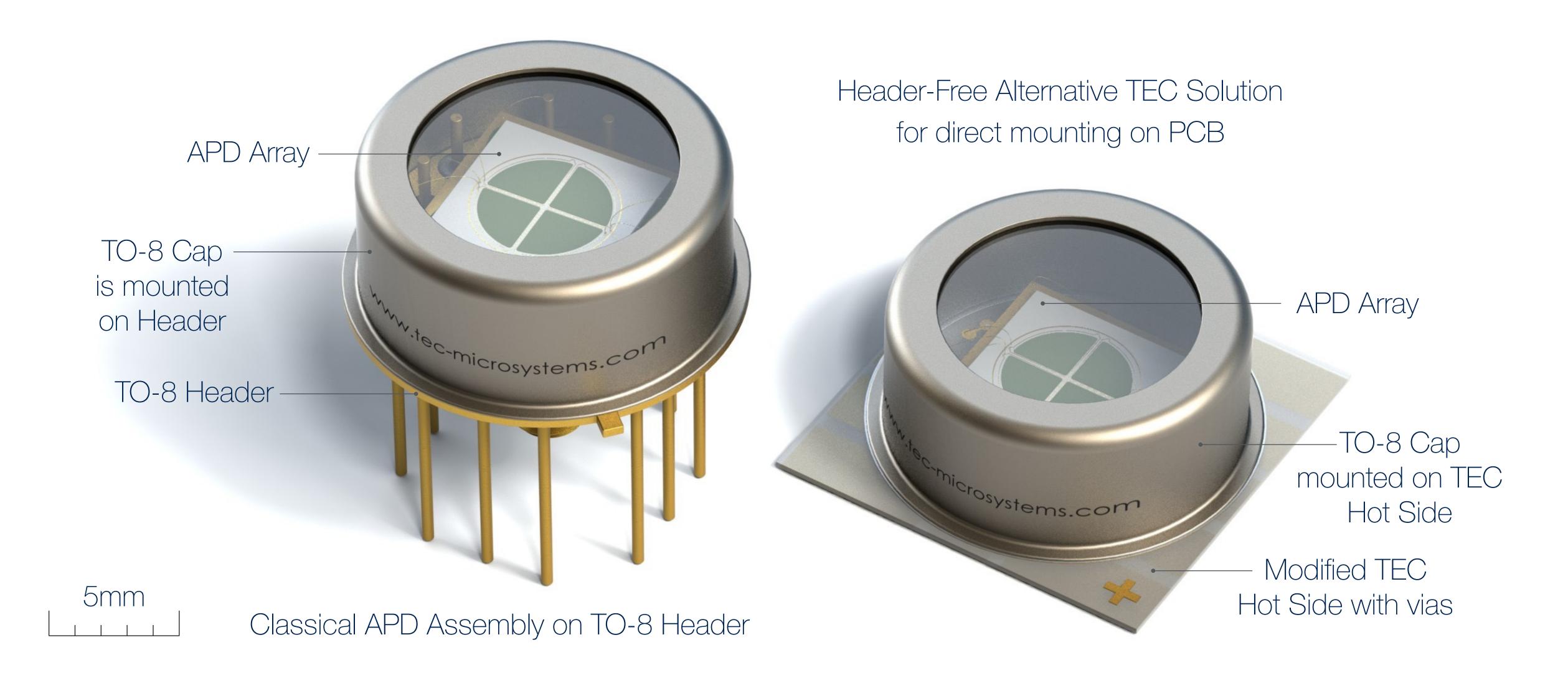

#### Header-free TEC Solution for APD Applications (Concept)

Any TEC can be modified for Header-Free Solution. Flexible configurations for Single APD and APD Arrays

Copyright TEC Microsystems GmbH. Images by Tim Gromov. Images contain hidden watermarks.

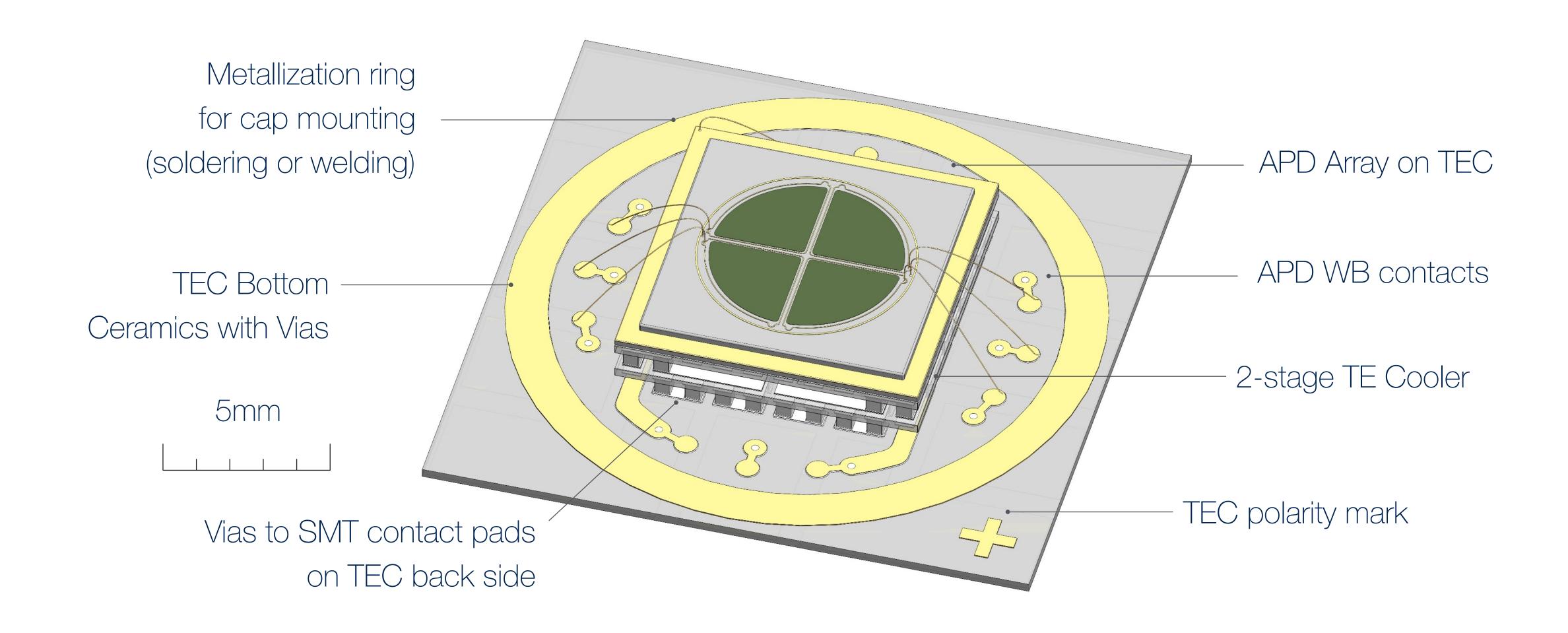

#### Header-free TEC Solution for APD Applications (Concept)

### Header-free TEC Solution for APD Applications (Concept)

TE Cooler Bottom Ceramics is optimized for SMT mounting using VIAS

SMT TEC surface can be developed in accordance to application requirements (size, number of vias and etc)

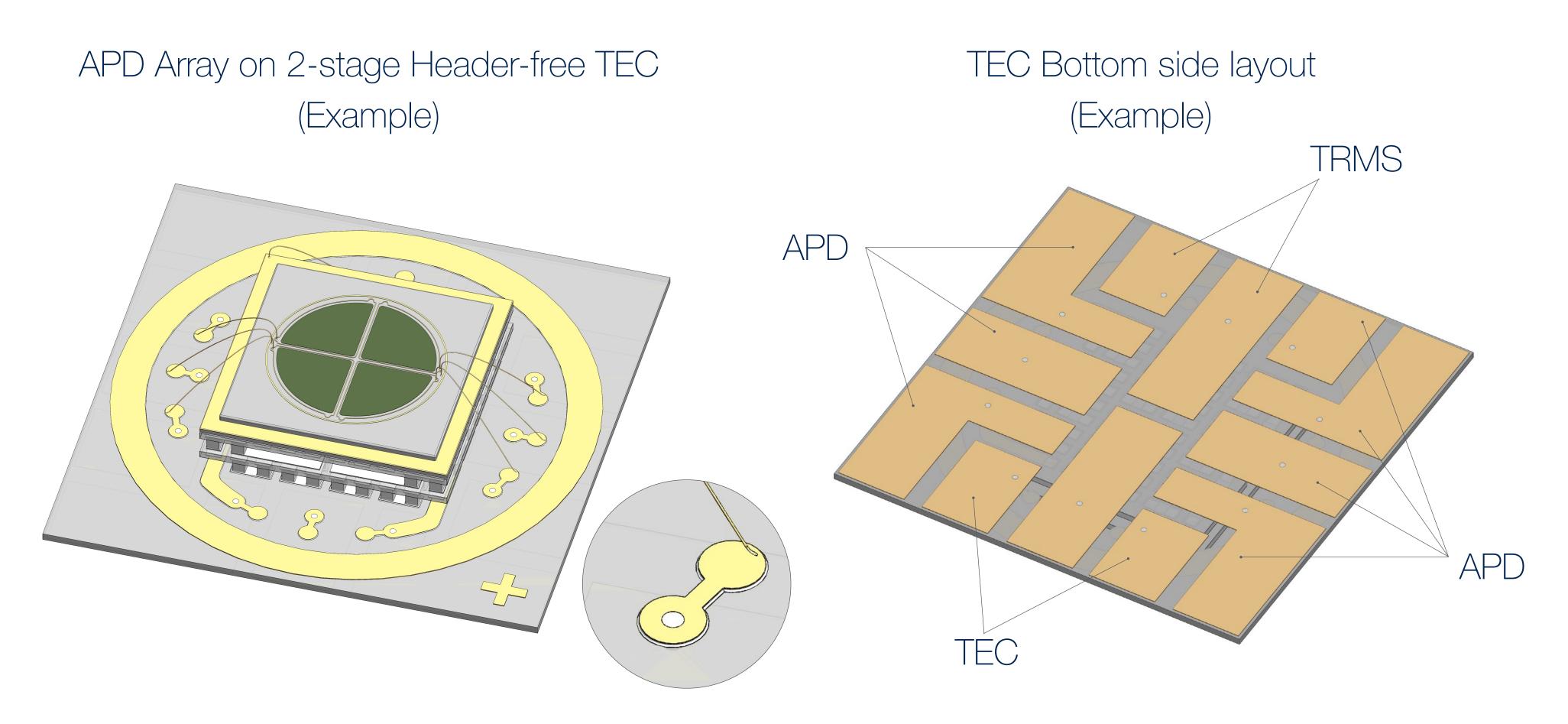

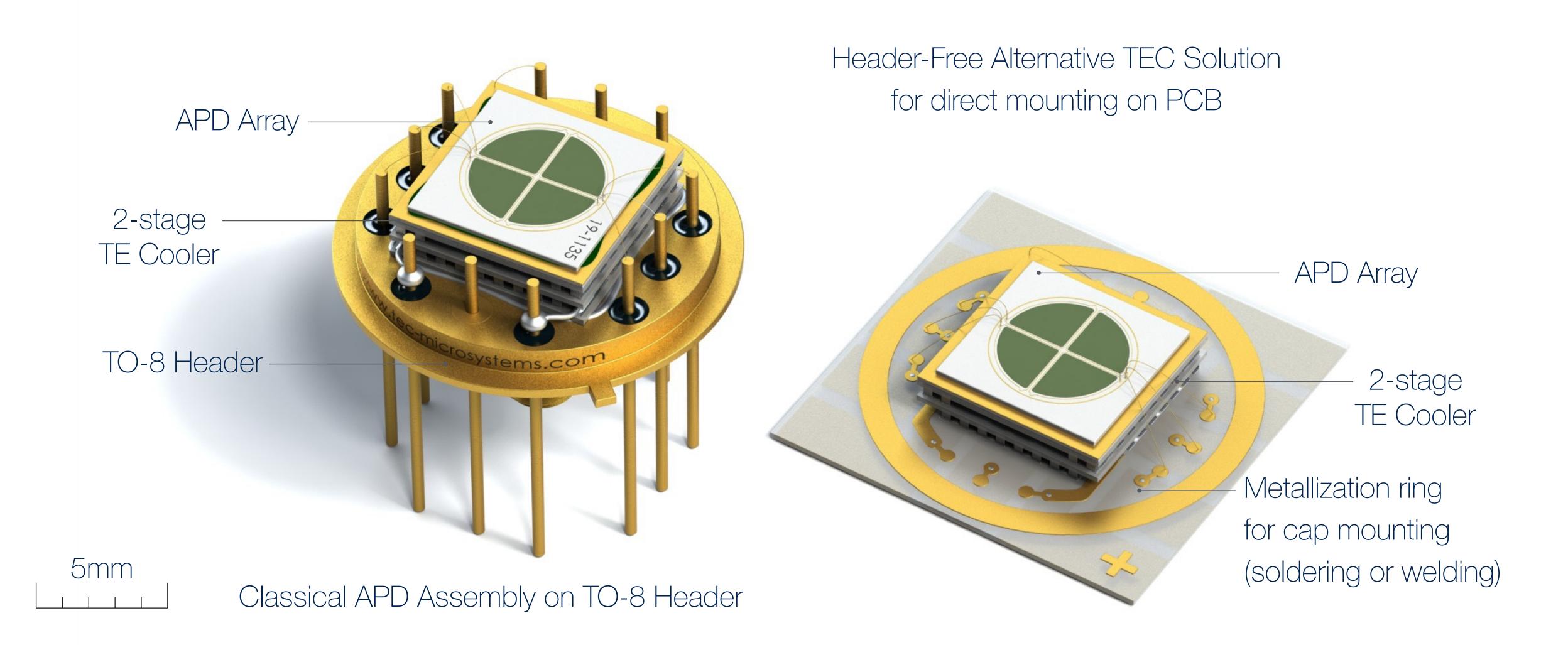

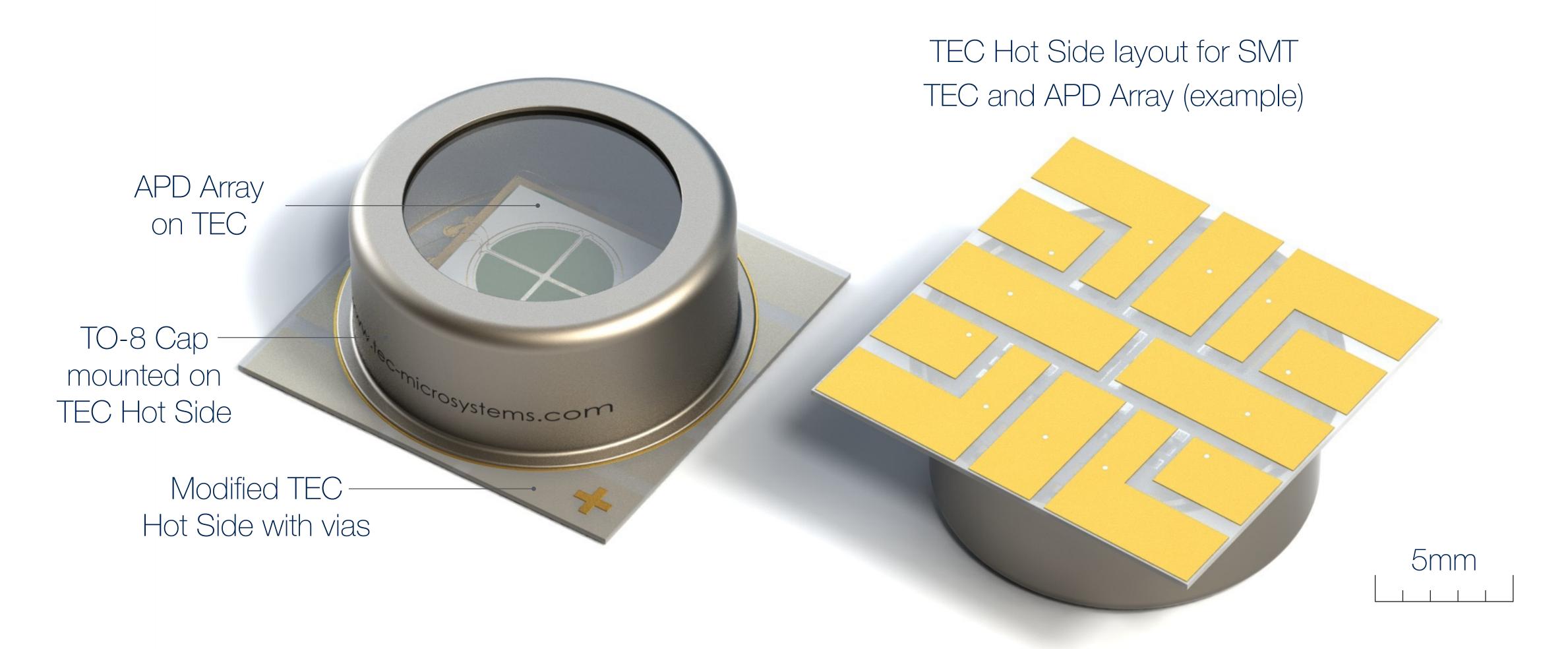

# Header-free TEC Solution for APD Applications (Example)

## Header-free TEC Solution for APD Applications (Example)

## Header-free TEC Solution for APD Applications (Example)

SMT surface can be developed in accordance to application requirements (size, number of vias and etc)